Usted podría hacer fácilmente un DDS altamente flexible en una placa de descubrimiento STM32F4 por aproximadamente $ 15 usando un DAC interno, un DMA, un temporizador y una tabla de búsqueda de seno. La gente ha publicado ejemplos de cosas similares en el blog si los buscas.

Para obtener la frecuencia requerida (los DAC STM32F4xx solo pueden hacer 300 cps en el swing completo, lo que equivale a ~ 1V / \ $ \ mu \ $ s) tendrá que restringir el rango del DAC.

Para una sinusoide, la velocidad de giro máxima (en V / s) es \ $ 2 \ pi \ veces f \ veces A \ $.

Insertar los valores de los requisitos del OP y suponiendo que Vref del DAC es 3.3V (que si recuerdo correctamente es el caso de un STM32F4Disco), una onda sinusoidal de 3.3Vpp a 100kHz, la velocidad de giro máxima es \ $ 2 \ pi \ veces 10 ^ 5 \ times 3.3 / 2 = 1036726 \ $ V / s, o \ $ \ approx1.04 \ $ V / \ $ \ mu \ $ s.

Para cumplir con esta restricción, la amplitud de la onda sinusoidal debe limitarse, de \ $ 3.3 \ $ V a \ $ 3.3 \ veces 1 / 1.04 = 3.18 \ $ V.

Esto trae ahora el problema aparente del límite de 300 cps en el DAC STM32F4. Ese límite es un furphy. No sé cuál es el límite superior físico real, pero sospecho que es la velocidad del bus APB1. Sé (porque lo he hecho) que puede escribir al menos 2Msps en el DAC y siempre que respete la velocidad de respuesta de 1V / us, se comportará de manera predecible. Por lo tanto, puede hacer 16 muestras por ciclo para una onda sinusoidal de 100 kHz, una velocidad de actualización de 1.6Msps, siempre y cuando limite la amplitud de la onda sinusoidal a 3.18 V en lugar de 3.3 V.

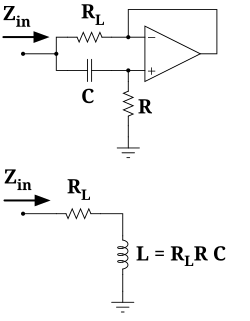

En algún momento, es probable que tenga que lidiar con potenciómetros digitales porque la realidad es que si desea una señal de salida continua y suave, especialmente a baja velocidad, tendrá que ejecutar su DDS a través de un filtro, y ese filtro tendrá que ser ajustable, no se puede simplemente colocar un LPF de 100 kHz y esperar que sea útil en las frecuencias de menos de 1 Hz.