La razón por la que la DRAM tarda más en escribir se debe a la naturaleza sensible del bit DRAM y la forma en que están cableadas las matrices. Esencialmente, estos dos parámetros hacen que sea necesario realizar una lectura antes de escribir cualquier información.

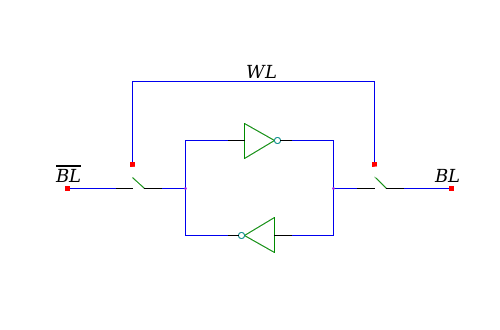

Las matrices de memoria, incluida la DRAM, generalmente se organizan en una cuadrícula. Las salidas de cada bit están conectadas verticalmente, y las señales de habilitación para cada bit están conectadas horizontalmente. Para leer un poco de datos, la señal de habilitación horizontal, o línea de palabra, conecta toda la fila a los cables verticales conocidos como líneas de bits. Incluso si solo desea un solo bit en una matriz grande, debe acceder a toda la fila. Esta flexibilidad reducida en el enrutamiento es necesaria para lograr la densidad deseada en las matrices de memoria.

DRAM es esencialmente una serie de condensadores con interruptores. Cuando se diseñan estos condensadores, son solo una fracción de las capacidades parásitas de cableado de las líneas de bits verticales. Los amplificadores conectados a las líneas de bits pueden detectar el pequeño cambio de voltaje que se produce cuando se conecta una celda DRAM cargada a la línea de bits y amplificarla en un valor lógico que otros circuitos y chips pueden usar. Debido a la carga compartida de la capacitancia de la línea de bits y la capacidad de la celda DRAM, los datos en un bit de DRAM se borran efectivamente cada vez que se accede a ellos. Si desea leer un solo bit de DRAM, debe volver a escribir el valor en el mismo bit. Por lo tanto, cada vez que lee desde DRAM, el ciclo se lee, luego se escribe.

Debido a la naturaleza de la cuadrícula de las matrices de memoria, el número de bits en una fila suele ser mucho mayor que el tamaño de palabra de la matriz. Esto significa que si desea leer o escribir una palabra de una fila, habrá bits que se activarán por la línea de palabra que no quiso leer o escribir. Estos datos serán destruidos si no se hace nada para preservarlos. Eso significa que cuando lees, debes leer toda la fila y escribir toda la fila. Para escribir, debe leer toda la fila y luego volver a escribir los datos que lee junto con los datos que desea escribir. Por lo tanto, el procedimiento para escribir datos en la matriz se lee, luego se escribe.

Así que vemos que el procedimiento es esencialmente el mismo tanto para leer como para escribir: primero lea una fila y luego vuelva a escribir los nuevos contenidos. La lectura se realiza primero, por lo que los datos podrían estar disponibles primero si el proceso es un evento de varios ciclos. La escritura puede llevar más tiempo, ya que la escritura no se produce hasta el final del proceso. Históricamente, esto puede haber sido un proceso de varios ciclos, pero he visto amplificadores para leer que responderán tan pronto como conozcan el valor que lo convierte en un vínculo para leer y escribir.