Hace un par de años leí un interesante artículo de Wikipedia sobre algo que se llama una "matriz de puertas programables en campo". El artículo hizo que pareciera que es una caja de lógica que puede conectar de forma arbitraria para implementar cualquier tipo de lógica que desee (pero sin necesidad de miles de componentes discretos).

Ahora, había asumido esto funciona como una PROM. Al igual que en, compras un dado que tiene todas las puertas, con todo conectado a todo, y luego hay una ventana de vidrio en el dado, y utilizas uno de esos escritores de rayos UV extremadamente caros para "quemar" a través de las conexiones. No quieres, lo que resulta en el circuito lógico que diseñaste. (Y tal vez hay una versión que también se puede borrar, como la forma en que se puede borrar un CD-RW). Una vez que haya "grabado" su programa en el chip, se comporta como si fuera la combinación real de puertas lógicas. (¡Porque ahora es esa combinación de puertas lógicas!)

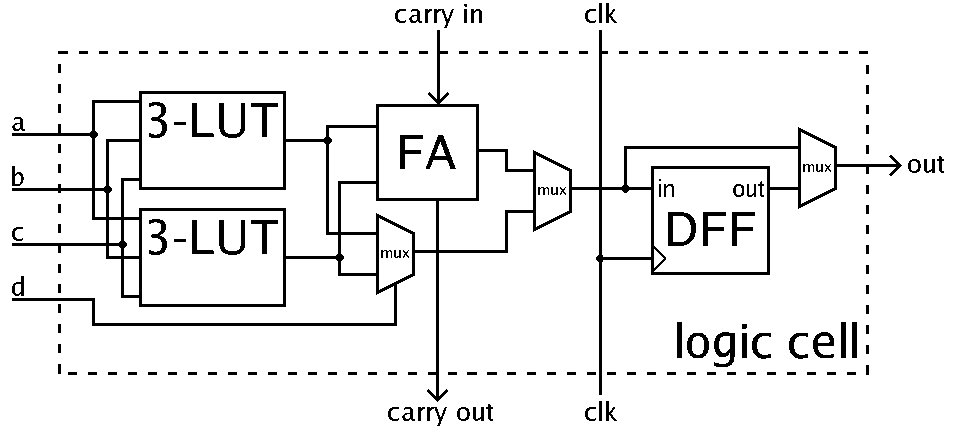

Sin embargo, más recientemente he estado leyendo sobre esto, y parece que no es así como funciona la tecnología. Muchos artículos recientes hablan de la necesidad de enviar un "flujo de bits" al FPGA en el encendido del sistema (e incluso la posibilidad de cifrar este flujo de bits para evitar que los competidores lo lean). Esto hace que suene de manera alarmante, como que un FPGA no es una construcción de hardware ; hace que parezca que realmente es solo un microprocesador común que está simulando su diseño en software.

En particular, eso significa que un diseño programado en un FPGA nunca puede ejecutarse más rápido que el microprocesador subyacente que lo está simulando. Lo que hace que todo el esfuerzo suene ... algo inútil. Pensé que todo el punto de un FPGA era hacer lógica personalizada que haga las cosas más rápido de lo que puedes hacerlo con el software. Pero todo este "flujo de bits" hace que parezca que es todavía un software ...

Estoy un poco confundido aquí. ¿Cómo funciona un FPGA en realidad ?