Fondo

Supongamos que tengo la siguiente situación ...

- PC con la NIC codificada a 100 Mbps, dúplex completo

- Cable RJ45, clavado EIA-568B (no es que los colores en el pinout importen)

- Cisco Catalyst 3560 Switch, que utiliza la autonegociación IEEE 802.3-1998 (solo 10 / 100Mbps)

Dado que la NIC de la PC está bloqueada a 100 / full, la negociación automática de Ethernet de Cisco falla y vuelve a 100 / half. Ahora hay un desajuste dúplex en la línea. Ahora, asumamos que la PC y Cisco transmiten exactamente en el mismo instante.

LOGICAL DIAGRAM

===============

Tx Tx

100/full -----> <----- 100/half

PC ------------------------------------- Cisco Catalyst 3560

PHYSICAL LAYER

==============

Tx D1 Tx on Rx D2??

-----> <------

568B 568B

Pin Signal Pin Signal

1 TX+ D1 --------------------------- 3 RX+ D2

2 TX- D1 --------------------------- 6 RX- D2

3 RX+ D2 --------------------------- 1 TX+ D1

6 RX- D2 --------------------------- 2 TX- D1

<------

Tx D1

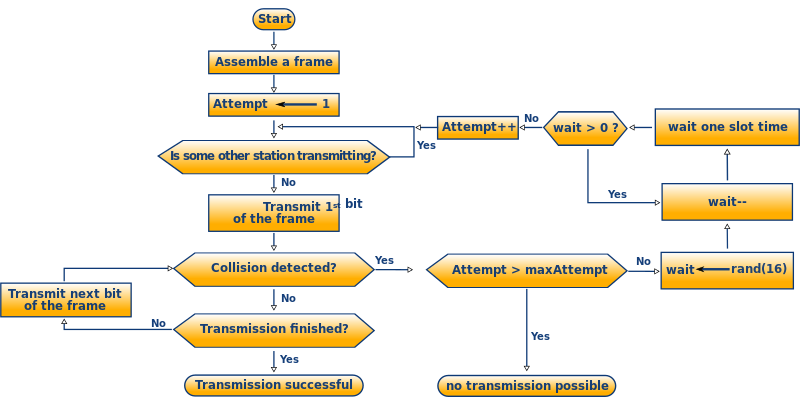

El diagrama de flujo de CSMA / CD se ve así ...

Mis preguntas están específicamente en el bloque de decisión para "¿Alguna otra estación está transmitiendo?" ¿Cómo funciona exactamente esto en la capa física?

Preguntas:

- Considere el diagrama de la CAPA FÍSICA. Cuando Cisco transmite a 100 / la mitad, ¿solo transmite en los pines 1 y 2 (marcado Tx D1)? La intuición dice que esto es cierto, pero quiero asegurarme de que entiendo cómo un Ether PHY de 100BaseT < a href="http://en.wikipedia.org/wiki/Carrier_sense_multiple_access_with_collision_detection"> CSMA / CD funciona. Considero que es posible que Half-duplex se configure para transmitir en los cuatro pines (Tx D1 y Rx D2) ya que he escuchado que the tx el conductor de línea inspecciona la señal transmitida para detectar colisiones.

- Si Cisco solo transmite en 1 y 2 (Tx D1), el Ether PHY se registra ¿La colisión porque detecta la transmisión de la PC en los pines 3 y 6 (Rx D2)? Para mí, es contra-intuitivo registrar una colisión si tienes un par de Rx dedicado.

Por favor, cita referencias de estándares para respuestas.